INTERNATIONAL TELECOMMUNICATION UNION

**I.430**

TELECOMMUNICATION STANDARDIZATION SECTOR OF ITU (11/95)

# INTEGRATED SERVICES DIGITAL NETWORK (ISDN) ISDN USER-NETWORK INTERFACES

# BASIC USER-NETWORK INTERFACE – LAYER 1 SPECIFICATION

# **ITU-T** Recommendation I.430

(Previously "CCITT Recommendation")

## FOREWORD

The ITU-T (Telecommunication Standardization Sector) is a permanent organ of the International Telecommunication Union (ITU). The ITU-T is responsible for studying technical, operating and tariff questions and issuing Recommendations on them with a view to standardizing telecommunications on a worldwide basis.

The World Telecommunication Standardization Conference (WTSC), which meets every four years, establishes the topics for study by the ITU-T Study Groups which, in their turn, produce Recommendations on these topics.

The approval of Recommendations by the Members of the ITU-T is covered by the procedure laid down in WTSC Resolution No. 1 (Helsinki, March 1-12, 1993).

ITU-T Recommendation I.430 was revised by ITU-T Study Group 13 (1993-1996) and was approved under the WTSC Resolution No. 1 procedure on the 2nd of November 1995.

\_\_\_\_\_

#### NOTE

In this Recommendation, the expression "Administration" is used for conciseness to indicate both a telecommunication administration and a recognized operating agency.

#### © ITU 1996

All rights reserved. No part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the ITU.

# CONTENTS

| Servic | e characte  | eristics                                   |

|--------|-------------|--------------------------------------------|

| 2.1    |             | s required from the physical medium        |

| 2.2    |             | provided to layer 2                        |

| 2.2    | 2.2.1       | Transmission capability                    |

|        | 2.2.1       | Activation/deactivation                    |

|        | 2.2.2       | D-channel access                           |

|        | 2.2.3       | Maintenance                                |

|        | 2.2.4       | Status indication                          |

| 2.3    |             | ves between layer 1 and the other entities |

|        |             | tion                                       |

| 3.1    | -           | p-point operation                          |

|        |             |                                            |

| 3.2    |             | p-multipoint operation                     |

| • •    | -           | configuration                              |

| 4.1    |             | p-point configuration                      |

| 4.2    |             | o-multipoint configuration                 |

| 4.3    | Wiring      | polarity integrity                         |

| 4.4    | Locatio     | n of the interfaces                        |

| 4.5    | NT and      | TE associated wiring                       |

| Functi | ional chara | acteristics                                |

| 5.1    |             | e functions                                |

|        | 5.1.1       | B-channel                                  |

|        | 5.1.2       | Bit timing                                 |

|        | 5.1.3       | Octet timing                               |

|        | 5.1.4       | Frame alignment                            |

|        | 5.1.5       | D-channel                                  |

|        | 5.1.6       | D-channel access procedure                 |

|        | 5.1.7       | Power feeding                              |

|        | 5.1.8       | Deactivation                               |

|        | 5.1.9       | Activation                                 |

| 5.2    | Intercha    | ange circuits                              |

| 5.3    | Connec      | ted/disconnected indication                |

|        | 5.3.1       | TEs powered across the interface           |

|        | 5.3.2       | TEs not powered across the interface       |

|        | 5.3.3       | Indication of connection status            |

| 5.4    | Frame s     | structure                                  |

|        | 5.4.1       | Bit rate                                   |

|        | 5.4.2       | Binary organization of the frame           |

| 5.5    | Line co     | de                                         |

| 5.6    | Timing      | considerations                             |

| Interf | ace proced  | lures                                      |

| 6.1    | -           | nel access procedure                       |

|        | 6.1.1       | Interframe (layer 2) time fill             |

|        | 6.1.2       | D-echo channel                             |

|        | 6.1.3       | D-channel monitoring                       |

|        |             | •                                          |

|        | 6.1.4       | Priority mechanism                         |

| 6.2   |             | ion/deactivation                                                       |

|-------|-------------|------------------------------------------------------------------------|

|       | 6.2.1       | Definitions                                                            |

|       | 6.2.2       | Signals                                                                |

|       | 6.2.3       | Activation/deactivation procedure for TEs                              |

|       | 6.2.4       | Activation/deactivation for NTs                                        |

|       | 6.2.5       | Timer values                                                           |

|       | 6.2.6       | Activation times                                                       |

|       | 6.2.7       | Deactivation times                                                     |

| 6.3   | Frame a     | lignment procedures                                                    |

|       | 6.3.1       | Frame alignment procedure in the direction NT to TE                    |

|       | 6.3.2       | Frame alignment in the direction TE to NT                              |

|       | 6.3.3       | Multiframing                                                           |

|       | 6.3.4       | S-channel structuring algorithm                                        |

| 6.4   | Idle cha    | nnel code on the B-channels                                            |

| Lave  | r 1 mainten | ance                                                                   |

| 7.1   |             | on for operational and maintenace functions between terminal and NT1   |

| /.1   | 7.1.1       | Introduction                                                           |

|       | 7.1.2       | Test loopbacks                                                         |

|       | 7.1.2       | Codes, message durations, and detection algorithms for a Q-channel and |

|       | 7.1.5       | SC1-subchannel                                                         |

|       | 7.1.4       | Code priorities for Q-channel and SC1-subchannel                       |

|       | 7.1.5       | TE-to-NT direction messages (Q bits)                                   |

|       | 7.1.6       | NT-to-TE direction messages (SC1 bits)                                 |

|       | 7.1.7       | B-channel loopback indications (LB1I, LB2I, LB1/2I)                    |

|       | 7.1.8       | Loss-of-received-signal indication (LRS)                               |

|       | 7.1.9       | Disruptive NT Operation Indication (DOI)                               |

| Elect |             | cteristics                                                             |

|       |             |                                                                        |

| 8.1   |             | NT 1 1                                                                 |

|       | 8.1.1       | Nominal rate                                                           |

|       | 8.1.2       | Tolerance                                                              |

| 8.2   |             | d bit-phase relationship between TE input and output                   |

|       | 8.2.1       | Test configurations                                                    |

|       | 8.2.2       | Timing extraction jitter                                               |

|       | 8.2.3       | Total phase deviation input to output                                  |

| 8.3   | •           | r characteristics                                                      |

| 8.4   | Termina     | ation of the line                                                      |

| 8.5   | Transm      | itter output characteristics                                           |

|       | 8.5.1       | Transmitter output impedance                                           |

|       | 8.5.2       | Test load impedance                                                    |

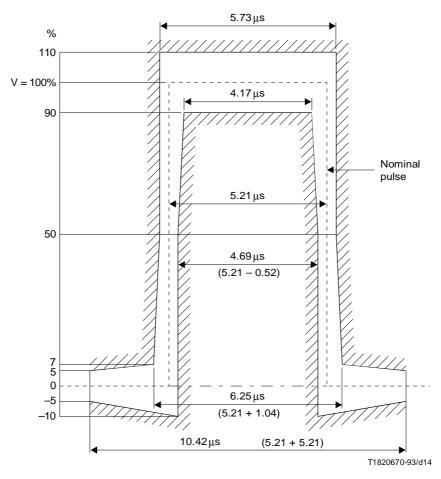

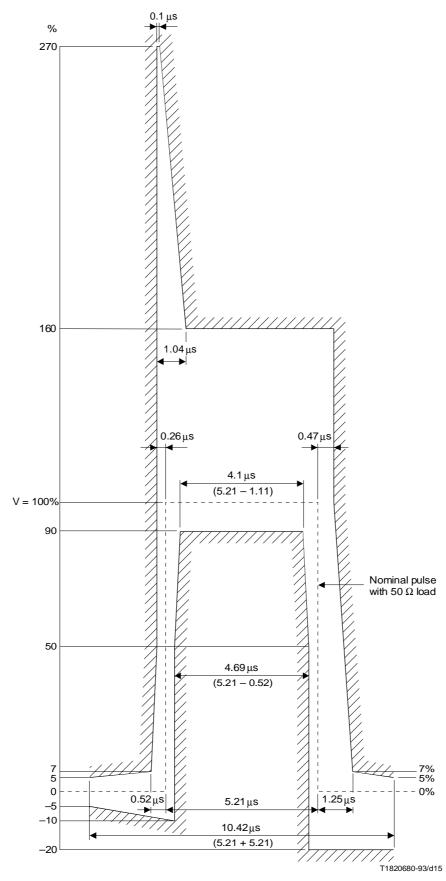

|       | 8.5.3       | Pulse shape and amplitude (binary ZERO)                                |

|       | 8.5.4       | Pulse unbalance                                                        |

|       | 8.5.5       | Voltage on other test loads (TE only)                                  |

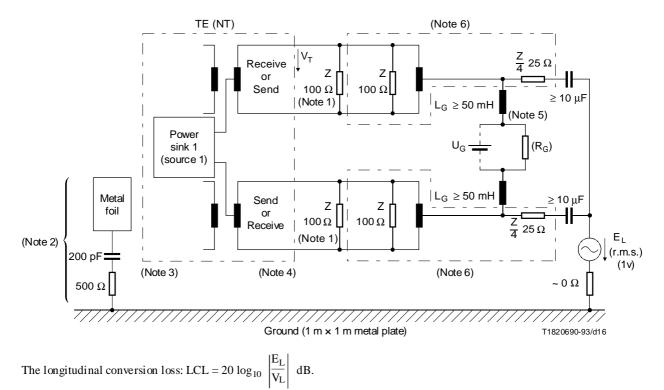

|       | 8.5.6       | Unbalance about earth                                                  |

| 8.6   | Receive     | er input characteristics                                               |

|       | 8.6.1       | Receiver input impedance                                               |

|       | 8.6.2       | Receiver sensitivity – Noise and distortion immunity                   |

|       | 8.6.3       | NT receiver input delay characteristics                                |

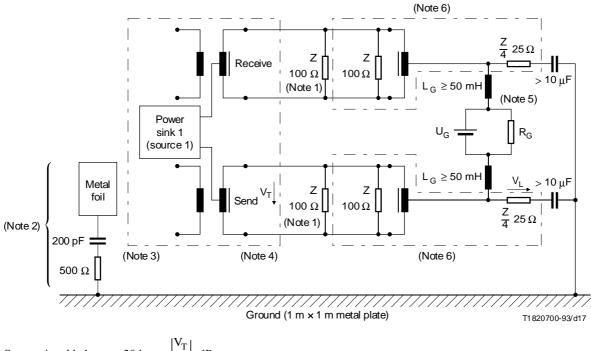

|       | 8.6.4       | Unbalance about earth                                                  |

| 8.7   |             | n from external voltages                                               |

| 8.8   |             | necting media characteristics                                          |

|       |             |                                                                        |

| 8.9   |             | d ISDN basic access TE cord                                            |

| 8.10  | -           | idinal output voltage                                                  |

| 8.11  | Electron    | magnetic compatibility (EMC)                                           |

| Power feeding |                  |                                                                                  |  |  |  |  |

|---------------|------------------|----------------------------------------------------------------------------------|--|--|--|--|

| 9.1           |                  | nce configuration                                                                |  |  |  |  |

|               | 9.1.1            | Functions specified at the access leads                                          |  |  |  |  |

|               | 9.1.2            | Provision of power sources and sinks                                             |  |  |  |  |

|               | 9.1.3            | Power feeding voltage                                                            |  |  |  |  |

| 9.2           |                  | available from NT                                                                |  |  |  |  |

|               | 9.2.1            | Power source 1 normal and restricted mode                                        |  |  |  |  |

|               | 9.2.2<br>9.2.3   | Voltage NT from power source 1                                                   |  |  |  |  |

|               | 9.2.3<br>9.2.4   | Voltage of power source 2                                                        |  |  |  |  |

| 0.2           |                  | *                                                                                |  |  |  |  |

| 9.3           | 9.3.1            | available at TE<br>Power consumption unit                                        |  |  |  |  |

|               | 9.3.1            | Power source 1 – Phantom powering                                                |  |  |  |  |

|               | 9.3.3            | Power source 2 – Optional third pair                                             |  |  |  |  |

| 9.4           |                  | rrent transient                                                                  |  |  |  |  |

| 9.5           |                  | ver consumption                                                                  |  |  |  |  |

| 9.5           | 9.5.1            | Power source 1                                                                   |  |  |  |  |

|               | 9.5.2            | Power source 2                                                                   |  |  |  |  |

| 9.6           |                  | ic isolation                                                                     |  |  |  |  |

| 9.0<br>9.7    |                  | ions on power source and sink during transient condition                         |  |  |  |  |

| 9.1           | 9.7.1            | Current/time limitations for TEs                                                 |  |  |  |  |

|               | 9.7.2            | Power source switchover time (PS1 or PS2)                                        |  |  |  |  |

|               | 9.7.2            | Other TE requirements                                                            |  |  |  |  |

|               | 9.7.4            | Other power source requirements                                                  |  |  |  |  |

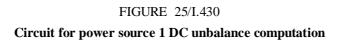

| 9.8           | PS1 dir          | ect current unbalance                                                            |  |  |  |  |

| 2.0           | 9.8.1            | TE requirements                                                                  |  |  |  |  |

|               | 9.8.2            | NT requirements                                                                  |  |  |  |  |

| 9.9           | Additic          | onal requirements for an auxiliary power supply (APS)                            |  |  |  |  |

|               | 9.9.1            | Power available from an APS                                                      |  |  |  |  |

|               | 9.9.2            | APS switch-on time                                                               |  |  |  |  |

|               | 9.9.3            | APS switch-off time                                                              |  |  |  |  |

|               | 9.9.4            | APS power consumption when off                                                   |  |  |  |  |

|               | 9.9.5            | Dynamic behaviour of APS                                                         |  |  |  |  |

| 9.10          | Additic          | onal requirements for NT1 restricted mode source for compatibility with an APS   |  |  |  |  |

|               | 9.10.1           | PS1 restricted mode back-off                                                     |  |  |  |  |

|               | 9.10.2           | PS1 restricted mode power-up                                                     |  |  |  |  |

|               | 9.10.3           | NT1 power consumption from APS normal mode                                       |  |  |  |  |

| Interfa       | ace conne        | ctor contact assignments                                                         |  |  |  |  |

|               | -                | configurations and round trip delay considerations used as a basis for electrica |  |  |  |  |

| A.1           | Introdu          | ction                                                                            |  |  |  |  |

| A.2           | Wiring           | configurations                                                                   |  |  |  |  |

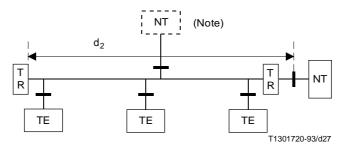

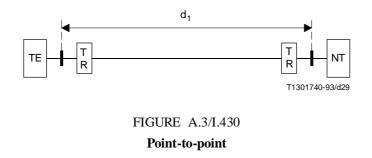

|               | A.2.1            | Point-to-multipoint                                                              |  |  |  |  |

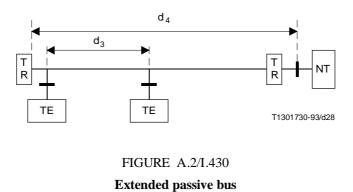

|               | A.2.2            | Point-to-point (Figure A.3)                                                      |  |  |  |  |

| nex B – S     | DL repres        | entation of a possible implementation of the D-channel access                    |  |  |  |  |

| nex C         |                  |                                                                                  |  |  |  |  |

|               |                  | uration                                                                          |  |  |  |  |

|               |                  |                                                                                  |  |  |  |  |

| I.1           | -                | nethods                                                                          |  |  |  |  |

| 1.1           | Introdu<br>I.1.1 | ction<br>Basic assumptions for test                                              |  |  |  |  |

| I.2           |                  | nel tests                                                                        |  |  |  |  |

| 1.2           | I.2.1            | D-echo channel                                                                   |  |  |  |  |

|               | 1.4.1            |                                                                                  |  |  |  |  |

iii

|      | I.3        | Interfa   | ce procedure tests                                                | ••••• |

|------|------------|-----------|-------------------------------------------------------------------|-------|

|      |            | I.3.1     | Activation/Deactivation procedures                                |       |

|      |            | I.3.2     | Timer for activation/deactivation                                 |       |

|      | I.4        | TE jitte  | er characteristics                                                | ••••• |

|      |            | I.4.1     | TE jitter measurement characteristics                             |       |

|      |            | I.4.2     | TE output phase offset                                            |       |

|      | I.5        | Pulse s   | shape and amplitude                                               |       |

|      |            | I.5.1     | Pulse shape                                                       |       |

|      |            | I.5.2     | Pulse unbalance test                                              | ••••• |

|      | I.6        | Termir    | nal power feeding dynamic requirements                            |       |

|      |            | I.6.1     | Test of TE start-up                                               |       |

|      |            | I.6.2     | Current transient                                                 |       |

|      |            | I.6.3     | Current/Time limitations for TEs                                  |       |

|      |            | I.6.4     | Protection against short-term interruptions                       |       |

|      |            | I.6.5     | TE Behaviour at switchover                                        |       |

|      |            | I.6.6     | Behaviour at low input voltage                                    |       |

|      | I.7        | Power     | source dynamic requirements                                       |       |

|      |            | I.7.1     | Power source type                                                 |       |

|      |            | I.7.2     | Restricted mode requirements for type a) sources only             |       |

|      |            | I.7.3     | Normal mode requirements for type a) sources only                 |       |

|      |            | I.7.4     | Restricted mode requirements for both type a) and type b) sources |       |

|      |            | I.7.5     | Normal mode requirements for both type a) and type b) sources     |       |

|      |            | I.7.6     | Power source switchover                                           |       |

|      |            | I.7.7     | PS1 restricted mode power-up                                      |       |

|      | I.8        | APS D     | Dynamic requirements                                              |       |

|      |            | I.8.1     | APS Switch-on time                                                |       |

|      |            | I.8.2     | APS switch-off time                                               |       |

|      | I.9        | Testing   | g for current unbalance                                           |       |

| Appe | endix II - | - Guideli | nes for implementation                                            |       |

|      | II.1       |           | feeding                                                           |       |

|      |            | II.1.1    | Introduction                                                      |       |

|      |            | II.1.2    | Power consumption                                                 |       |

|      |            | II.1.3    | General assumptions                                               |       |

|      |            | II.1.4    | Power source ripple                                               |       |

|      |            | II.1.5    | Dynamic behaviour of power sources and sinks                      |       |

|      |            | II.1.6    | Power source design for improved performance                      |       |

|      |            | II.1.7    | TE design for improved performance                                |       |

|      | II.2       | Inform    | nation on activation and deactivation tables                      |       |

|      |            | II.2.1    | Operation of Timer T3                                             |       |

|      |            | II.2.2    | Connection status                                                 |       |

# SUMMARY

This Recommendation defines the layer 1 characteristics of the user-network interface at S- and T-reference points for basic rate ISDN as defined in Recommendation I.412.

It defines service characteristics, mode of operation, wiring configuration and functional characteristics. The transmission characteristics, frame structure, line code and activation procedure at the interface are specified to facilitate the access of user equipment to the 2B- + D-channel at a bit rate of 192 kbit/s.

The specification of the electrical transmission characteristics and the power feeding over the interface shall ensure portability of terminal equipment for basic rate ISDN.

## **BASIC USER-NETWORK INTERFACE – LAYER 1 SPECIFICATION**

(Malaga-Torremolinos, 1984; amended at Melbourne, 1988 and at Helsinki 1993; revised in 1995)

## 1 General

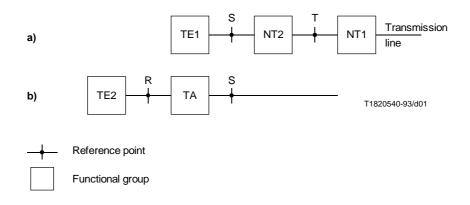

This Recommendation defines the layer 1 characteristics of the user-network interface to be applied at the S- or T-reference points for the basic interface structure defined in Recommendation I.412. The reference configuration for the interface is defined in Recommendation I.411 and is reproduced in Figure 1.

#### FIGURE 1/I.430

#### **Reference configurations for the ISDN user-network interfaces**

In this Recommendation, the term "NT" is used to indicate network terminating layer 1 aspects of NT1 and NT2 functional groups, and the term "TE" is used to indicate terminal terminating layer 1 aspects of TE1, TA and NT2 functional groups, unless otherwise indicated. However, in 6.2 only, the terms "NT" and "TE" have the following meaning: the term "NT" is used to indicate the layer 1 network side of the basic access interface; the term "TE" is used to indicate the layer 1 network side of the basic access interface; the term "TE" is used to indicate the layer 1 network side of the basic access interface.

Terms used in this Recommendation, together with their definitions, are contained in Recommendation I.112.

## 2 Service characteristics

#### 2.1 Services required from the physical medium

Layer 1 of this interface requires a balanced metallic transmission medium, for each direction of transmission, capable of supporting 192 kbit/s.

### 2.2 Service provided to layer 2

Layer 1 provides the following services to layer 2 and the management entity.

#### 2.2.1 Transmission capability

Layer 1 provides the transmission capability, by means of appropriately encoded bit streams, for the B- and D-channels and the related timing and synchronization functions.

## 2.2.2 Activation/deactivation

Layer 1 provides the signalling capability and the necessary procedures to enable customer TEs and/or NTs to be deactivated when required and reactivated when required. The activation and deactivation procedures are defined in 6.2.

#### 2.2.3 D-channel access

Layer 1 provides the signalling capability and the necessary procedures to allow TEs to gain access to the common resource of the D-channel in an orderly fashion while meeting the performance requirements of the D-channel signalling system. These D-channel access control procedures are defined in 6.1.

#### 2.2.4 Maintenance

Layer 1 provides the signalling capability, procedures and necessary functions at layer 1 to enable maintenance functions to be performed.

## 2.2.5 Status indication

Layer 1 provides an indication to the higher layers of the status of layer 1.

## 2.3 Primitives between layer 1 and the other entities

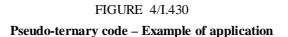

Primitives represent, in an abstract way, the logical exchange of information and control between layer 1 and other entities. They neither specify nor constrain the implementation of entities or interfaces.

The primitives to be passed across the layer 1/2 boundary or to the management entity and parameter values associated with these primitives are defined and summarized in Table 1. For description of the syntax and use of the primitives, refer to Recommendation X.211 and relevant detailed descriptions in clause 6.

#### TABLE 1/I.430

#### Primitives associated with layer 1

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Specific name |            | Parameter             |                 |                                                            |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|-----------------------|-----------------|------------------------------------------------------------|--|

| Generic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Request       | Indication | Priority<br>indicator | Message<br>unit | Message unit content                                       |  |

| $L1 \leftrightarrow L2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |            |                       |                 |                                                            |  |

| PH-DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | X<br>(Note 1) | Х          | X<br>(Note 2)         | Х               | Layer 2 peer-to-peer message                               |  |

| PH-ACTIVATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Х             | Х          | _                     | _               |                                                            |  |

| PH-DEACTIVATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _             | Х          | _                     | _               |                                                            |  |

| $M \leftrightarrow L1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |            |                       |                 |                                                            |  |

| MPH-ERROR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _             | Х          | _                     | Х               | Type of error or recovery from a previously reported error |  |

| MPH-ACTIVATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _             | Х          | _                     | _               |                                                            |  |

| MPH-DEACTIVATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Х             | Х          | _                     | _               |                                                            |  |

| MPH-INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _             | Х          | _                     | Х               | Connected/disconnected                                     |  |

| NOTES         1       PH-DATA request implies underlying negotiation between layer 1 and layer 2 for the acceptance of the data.         2       Dividual linear |               |            |                       |                 |                                                            |  |

2 Priority indication applies only to the request type.

# **3** Modes of operation

Both point-to-point and point-to-multipoint modes of operation, as described below, are intended to be accommodated by the layer 1 characteristics of the user-network interface. In this Recommendation, the modes of operation apply only to the layer 1 procedural characteristics of the interface and do not imply any constraints on modes of operation at higher layers.

## 3.1 **Point-to-point operation**

Point-to-point operation at layer 1 implies that only one source (transmitter) and one sink (receiver) are active at any one time in each direction of transmission at an S- or T-reference point. (Such operation is independent of the number of interfaces which may be provided on a particular wiring configuration – see clause 4.)

## **3.2 Point-to-multipoint operation**

Point-to-multipoint operation at layer 1 allows more than one TE (source and sink pair) to be simultaneously active at an S- or T-reference point. (The multipoint mode of operation may be accommodated, as discussed in clause 4, with point-to-point or point-to-multipoint wiring configurations.)

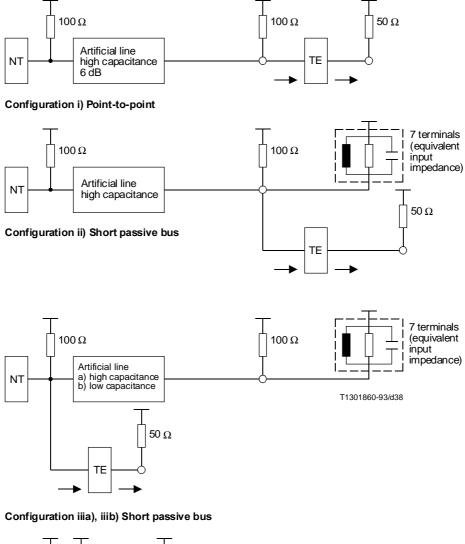

# **4** Types of wiring configuration

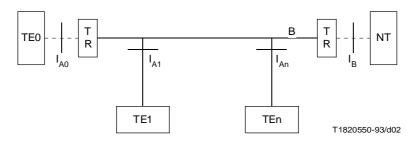

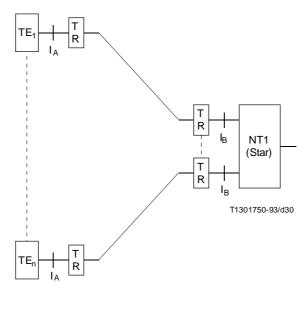

The electrical characteristics of the user-network interface are determined on the basis of certain assumptions about the various wiring configurations which may exist in the user premises. These assumptions are identified in two major configuration descriptions, 4.1 and 4.2, together with additional material contained in Annex A. Figure 2 shows a general reference configuration for wiring in the user premises.

## 4.1 **Point-to-point configuration**

A point-to-point wiring configuration implies that only one source (transmitter) and one sink (receiver) are interconnected on an interchange circuit.

## 4.2 **Point-to-multipoint configuration**

A point-to-multipoint wiring configuration allows more than one source to be connected to the same sink or more than one sink to be connected to the same source on an interchange circuit. Such distribution systems are characterized by the fact that they contain no active logic elements performing functions (other than possibly amplification or regeneration of the signal).

## 4.3 Wiring polarity integrity

For a point-to-point wiring configuration, the two wires of the interchange circuit pair may be reversed. However, for point-to-multipoint wiring configuration, the wiring polarity integrity of the interchange circuit (TE-to-NT direction) must be maintained between TEs (see the reference configuration in Figure 21).

In addition, the wires of the optional pairs, which may be provided for powering, may not be reversed in either configuration.

## 4.4 Location of the interfaces

The wiring in the user premises is considered to be one continuous cable run with jacks for the TEs and NT attached directly to the cable or using stubs less than 1 metre in length. The jacks are located at interface points  $I_A$  and  $I_B$  (see Figure 2). One interface point,  $I_A$ , is adjacent to each TE. The other interface point  $I_B$ , is adjacent to the NT. However, in some applications, the NT may be connected to the wiring without the use of a jack or with a jack which accommodates multiple interfaces (e.g. when the NT is a port on a PBX). The required electrical characteristics (described in clause 8) for  $I_A$  and  $I_B$  are different in some aspects.

TR Terminating Resistor

Electrical Interface

B Location of I<sub>B</sub> when the Terminating Resistor (TR) is included in the NT

#### FIGURE 2/I.430

#### Reference configuration for wiring in the user premises location

#### 4.5 NT and TE associated wiring

The wiring from the TE or the NT to its appropriate jack affects the interface electrical characteristics. A TE, or an NT that is not permanently connected to the interface wiring, may be equipped with either of the following for connection to the interface point ( $I_A$  and  $I_B$ , respectively):

- a hard wired connecting cord (of not more than 10 metres in the case of a TE, and not more than 3 metres in the case of an NT) and a suitable plug; or

- a jack with a connecting cord (of not more than 10 metres in the case of a TE, and not more than 3 metres in the case of an NT) which has a suitable plug at each end.

Normally, the requirements of this Recommendation apply to the interface point ( $I_A$  and  $I_B$ , respectively), and the cord forms part of the associated TE or NT. However, as a national option, where the terminating resistors are connected internally to the NT, the connecting cord may be considered as an integral part of the interface wiring. In this case, the requirements of this Recommendation may be applied to the NT at the connection of the connecting cord to the NT. Note that the NT may attach directly to the interface wiring without a detachable cord. Also note that the connector, plug and jack used for the connection of the detachable cord to the NT is subject to standardization. (Refer to clause 10.)

Although a TE may be provided with a cord of less than 5 metres in length, it shall meet the requirements of this Recommendation with a cord having a minimum length of 5 metres. As specified above, the TE cord may be detachable. Such a cord may be provided as a part of the TE, or the TE may be designed to conform to the electrical characteristics specified in clause 8 with a standard ISDN basic access TE cord conforming to the requirements specified in 8.9 and having the maximum permitted capacitance.

The use of an extension cord, of up to 25 metres in length, with a TE is permitted but only on point-to-point wiring configurations. (The total attenuation of the wiring and of the cord in this case should not exceed 6 dB.)

## **5** Functional characteristics

The following subclauses show the functions for the interface.

## 5.1 Interface functions

## 5.1.1 B-channel

This function provides, for each direction of transmission, two independent 64 kbit/s channels for use as B-channels (as defined in Recommendation I.412).

## 5.1.2 Bit timing

This function provides bit (signal element) timing at 192 kbit/s to enable the TE and NT to recover information from the aggregate bit stream.

## 5.1.3 Octet timing

This function provides 8 kHz octet timing for the NT and TE.

## 5.1.4 Frame alignment

This function provides information to enable NT and TE to recover the time division multiplexed channels.

## 5.1.5 D-channel

This function provides, for each direction of transmission, one D-channel at a bit rate of 16 kbit/s, as defined in Recommendation I.412.

## 5.1.6 D-channel access procedure

This function is specified to enable TEs to gain access to the common resource of the D-channel in an orderly controlled fashion. The functions necessary for these procedures include an echoed D-channel at a bit rate of 16 kbit/s in the direction NT to TE. For the definition of the procedures relating to D-channel access see 6.1.

## 5.1.7 Power feeding

This function provides for the capability to transfer power across the interface. The direction of power transfer depends on the application. In a typical application, it may be desirable to provide for power transfer from the NT towards the TEs in order to, for example, maintain a basic telephony service in the event of failure of the locally provided power. (In some applications unidirectional power feeding or no power feeding at all, across the interface, may apply.) The detailed specification of power feeding capability is contained in clause 9.

#### 5.1.8 Deactivation

This function is specified in order to permit the TE and NT to be placed in a low power consumption mode when no calls are in progress. For TEs that are power fed across the interface from power source 1 and for remotely power fed NTs, deactivation places the functions that are so powered into a low power consumption mode (see clause 9). The procedures and precise conditions under which deactivation takes place are specified in 6.2. (For some applications it will be appropriate for NTs to remain in the active state all the time.)

## 5.1.9 Activation

This function restores all the functions of a TE or an NT, which may have been placed into a lower power consumption mode during deactivation, to an operating power mode (see clause 9), whether under normal or restricted conditions. The procedures and precise conditions under which activation takes place are defined in 6.2. (For some applications it will be appropriate for NTs to remain in the active state all the time.)

## 5.2 Interchange circuits

Two interchange circuits, one for each direction of transmission, shall be used to transfer digital signals across the interface. All of the functions described in 5.1, except for power feeding, shall be carried by means of a digitally multiplexed signal structured as defined in 5.4.

## 5.3 Connected/disconnected indication

The appearance/disappearance of power is the criterion used by a TE to determine whether it is connected/disconnected at the interface. This is necessary for terminal endpoint identifier TEI assignments according to the procedures described in Recommendation I.441.

A TE which considers itself connected, when unplugged, can cause duplication of TEI values after reconnection. When duplication occurs, procedures described in Recommendation I.441 will permit recovery.

### 5.3.1 TEs powered across the interface

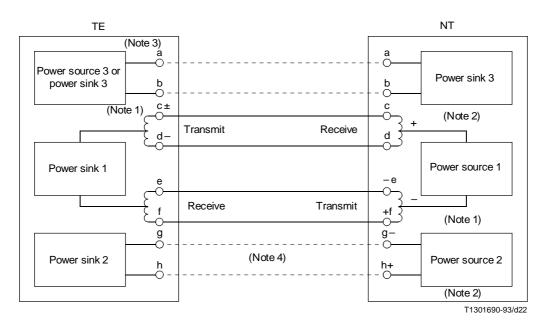

A TE which is powered from power source 1 or 2 across the interface shall use the detection of power source 1 or 2, respectively, to establish the connection status. (See clause 9 and Figure 21 for a description of the power sources.)

#### 5.3.2 TEs not powered across the interface

A TE which is not powered across the interface may use either:

- a) the detection of power source 1 or 2, whichever may be provided, to establish the connection status; or

- b) the presence/absence of local power to establish the connection status.

TEs which are not powered across the interface and are unable to detect the presence of power source 1 and 2 shall consider themselves connected/disconnected when local power is applied/removed.

NOTE – It is desirable to use the detection of power source 1 or 2 to establish the connection status when automatic TEI selection procedures are used within the management entity.

#### 5.3.3 Indication of connection status

TEs shall inform the management entity of their connection/disconnection status (for TEI purposes) using :

- a) MPH-INFORMATION indication (connected);

- b) MPH-INFORMATION indication (disconnected).

#### 5.4 Frame structure

In both directions of transmission, the bits shall be grouped into frames of 48 bits each. The frame structure shall be identical for all configurations (point-to-point and point-to-multipoint).

#### 5.4.1 Bit rate

The nominal transmitted bit rate at the interfaces shall be 192 kbit/s in both directions of transmission.

#### 5.4.2 Binary organization of the frame

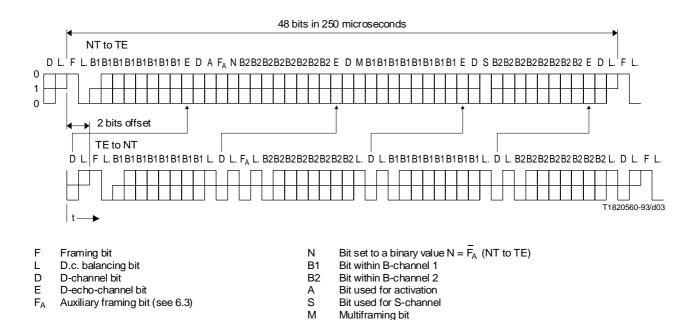

The frame structures are different for each direction of transmission. Both structures are illustrated diagrammatically in Figure 3.

#### 5.4.2.1 TE to NT

Each frame consists of the groups of bits shown in Table 2; each individual group is d.c.-balanced by its last bit (L bit).

#### 5.4.2.2 NT to TE

Frames transmitted by the NT contain an echo channel (E bits) used to retransmit the D bits received from the TEs. The D-echo channel is used for D-channel access control. The last bit of the frame (L bit) is used for balancing each complete frame.

The bits are grouped as shown in Table 3.

#### 5.4.2.3 Relative bit positions

At the TEs, timing in the direction TE to NT shall be derived from the frames received from the NT.

The first bit of each frame transmitted from a TE towards the NT shall be delayed, nominally, by two bit periods with respect to the first bit of the frame received from the NT. Figure 3 illustrates the relative bit positions for both transmitted and received frames.

#### 6 **Recommendation I.430** (11/95)

#### NOTES

- 1 Dots demarcate those parts of the frame that are independently d.c.-balanced.

- 2 The F<sub>A</sub> bit in the direction TE to NT is used as a Q bit in every fifth frame if the Q-channel capability is applied (see 6.3.3).

3 The nominal 2-bit offset is as seen from the TE ( $I_A$  in Figure 2). The corresponding offset at the NT may be greater due to delay in the interface cable and varies by configuration.

### FIGURE 3/I.430

#### Frame structure at reference points S and T

#### TABLE 2/I.430

| Bit position | Group                                                           |

|--------------|-----------------------------------------------------------------|

| 1 and 2      | Framing signal with balance bit                                 |

| 3 to 11      | B1-channel (first octet) with balance bit                       |

| 12 and 13    | D-channel bit with balance bit                                  |

| 14 and 15    | F <sub>A</sub> auxiliary framing bit for Q bit with balance bit |

| 16 to 24     | B2-channel (first octet) with balance bit                       |

| 25 and 26    | D-channel bit with balance bit                                  |

| 27 to 35     | B1-channel (second octet) with balance bit                      |

| 36 and 37    | D-channel bit with balance bit                                  |

| 38 to 46     | B2-channel (second octet) with balance bit                      |

| 47 and 48    | D-channel bit with balance bit                                  |

## TABLE 3/I.430

| Bit position      | Group                                                                                |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------|--|--|--|--|

| 1 and 2           | Framing signal with balance bit                                                      |  |  |  |  |

| 3 to 10           | B1-channel (first octet)                                                             |  |  |  |  |

| 11                | E-, D-echo channel bit                                                               |  |  |  |  |

| 12                | D-channel bit                                                                        |  |  |  |  |

| 13                | Bit A used for activation                                                            |  |  |  |  |

| 14                | FA auxiliary framing bit                                                             |  |  |  |  |

| 15                | N bit (coded as defined in 6.3)                                                      |  |  |  |  |

| 16 to 23          | B2-channel (first octet)                                                             |  |  |  |  |

| 24                | E-, D-echo channel bit                                                               |  |  |  |  |

| 25                | D-channel bit                                                                        |  |  |  |  |

| 26                | M, multiframing bit                                                                  |  |  |  |  |

| 27 to 34          | B1-channel (second octet)                                                            |  |  |  |  |

| 35                | E-, D-echo channel bit                                                               |  |  |  |  |

| 36                | D-channel bit                                                                        |  |  |  |  |

| 37                | S                                                                                    |  |  |  |  |

| 38 to 45          | B2-channel (second octet)                                                            |  |  |  |  |

| 46                | E-, D-echo channel bit                                                               |  |  |  |  |

| 47                | D-channel bit                                                                        |  |  |  |  |

| 48                | Frame balance bit                                                                    |  |  |  |  |

| NOTE – The use of | NOTE – The use of the S bit is optional, and when not used it is set to binary ZERO. |  |  |  |  |

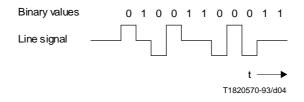

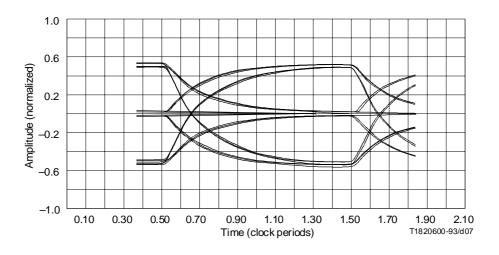

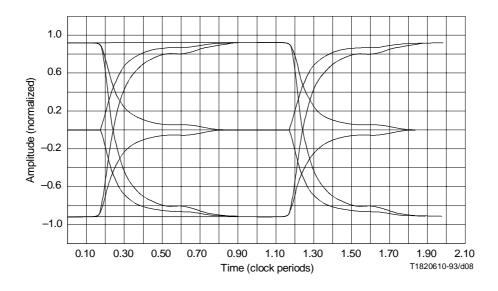

## 5.5 Line code

For both directions of transmission, pseudo-ternary coding is used with 100% pulse width as shown in Figure 4. Coding is performed in such a way that a binary ONE is represented by no line signal, whereas a binary ZERO is represented by a positive or negative pulse. The first binary ZERO following the frame bit-balance bit is of the same polarity as the framing bit-balance bit. Subsequent binary ZEROs must alternate in polarity.

A balance bit is a binary ZERO if the number of binary ZEROs following the previous balance bit is odd. A balance bit is a binary ONE if the number of binary ZEROs following the previous balance bit is even.

## 5.6 Timing considerations

The NT shall derive its timing from the network clock. A TE shall derive its timing (bit, octet, frame) from the signal received from the NT and use this derived timing to synchronize its transmitted signal.

## 6 Interface procedures

### 6.1 D-channel access procedure

The following procedure allows for a number of TEs connected in a multipoint configuration to gain access to the D-channel in an orderly fashion. The procedure always ensures that, even in cases where two or more TEs attempt to access the D-channel simultaneously, one, but only one, of the TEs will be successful in completing transmission of its information. This procedure relies upon the use of layer 2 frames delimited by flags consisting of the binary pattern "01111110" and the use of zero bit insertion to prevent flag imitation (see Recommendation I.441).

The procedure also permits TEs to operate in a point-to-point manner.

#### 6.1.1 Interframe (layer 2) time fill

When a TE has no layer 2 frames to transmit, it shall send binary ONEs on the D-channel, i.e. the interframe time fill in the TE-to-NT direction shall be binary ONEs.

When an NT has no layer 2 frames to transmit, it shall send binary ONEs or HDLC flags, i.e. the interframe time fill in the NT-to-TE direction shall be either all binary ONEs or repetitions of the octet "01111110". When the interframe time fill is HDLC flags, the flag which defines the end of a frame may define the start of the next frame.

#### 6.1.2 D-echo channel

The NT, on receipt of a D-channel bit from TE or TEs, shall reflect the binary value in the next available D-echo channel bit position towards the TE. (It may be necessary to force the D-echo channel bits to all binary ZEROs during certain loopbacks.)

#### 6.1.3 D-channel monitoring

A TE, while in the active condition, shall monitor the D-echo channel, counting the number of consecutive binary ONEs. If a binary ZERO bit is detected, the TE shall restart counting the number of consecutive binary ONE bits. The current value of the count is called C.

NOTE - C need not be incremented after the value eleven has been reached.

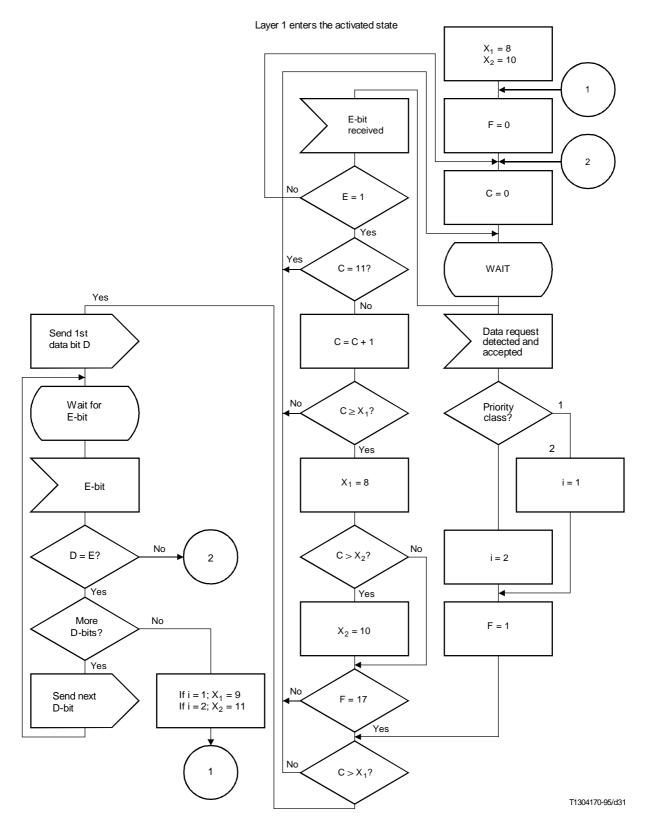

#### 6.1.4 Priority mechanism

Layer 2 frames are transmitted in such a way that signalling information is given priority (priority class 1) over all other types of information (priority class 2). Furthermore, to ensure that within each priority class all competing TEs are given a fair access to the D-channel, once a TE has successfully completed the transmission of a frame, it is given a lower level of priority within the class. The TE is given back its normal level within a priority class when all TEs have had an opportunity to transmit information at the normal level within that priority class.

The priority class of a particular layer 2 frame may be a characteristic of the TE which is preset at manufacture or at installation, or it may be passed down from layer 2 as a parameter of the PH-DATA request primitive.

The priority mechanism is based on the requirement that a TE may start layer 2 frame transmission only when C (see 6.1.3) is equal to, or exceeds, the value  $X_1$  for priority class 1 or is equal to, or exceeds, the value  $X_2$  for priority class 2. The value of  $X_1$  shall be eight for the normal level and nine for the lower level of priority. The value of  $X_2$  shall be ten for the normal level and eleven for the lower level of priority.

In a priority class the value of the normal level of priority is changed into the value of the lower level of priority (i.e. higher value) when a TE has successfully transmitted a layer 2 frame of that priority class.

The value of the lower level of priority is changed back to the value of the normal level of priority when C (see 6.1.3) equals the value of the lower level of priority (i.e. higher value).

## 6.1.5 Collision detection

While transmitting information in the D-channel, the TE shall monitor the received D-echo channel and compare the last transmitted bit with the next available D-echo bit. If the transmitted bit is the same as the received echo, the TE shall continue its transmission. If, however, the received echo is different from the transmitted bit, the TE shall cease transmission immediately and return to the D-channel monitoring state.

## 6.1.6 **Priority system**

Annex B describes an example of how the priority system may be implemented.

## 6.2 Activation/deactivation

## 6.2.1 Definitions

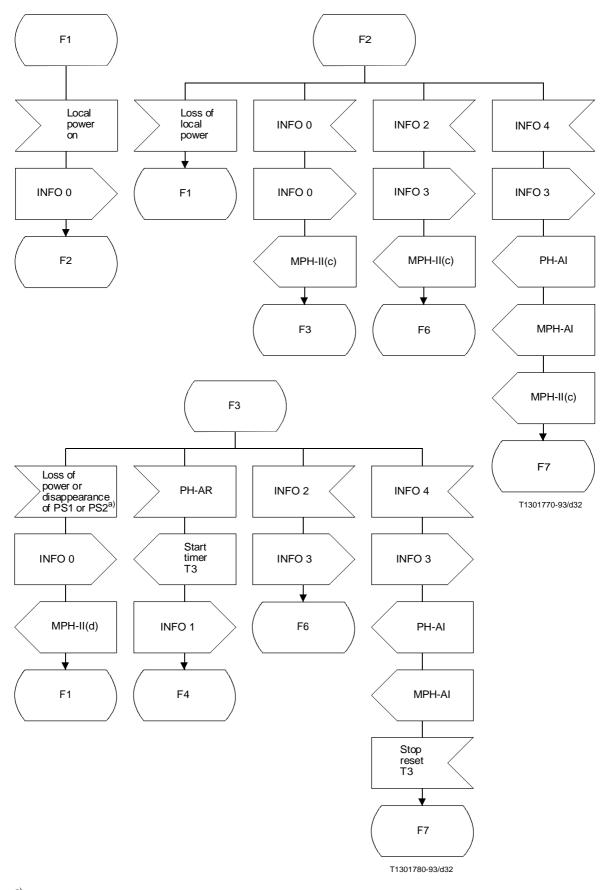

## 6.2.1.1 TE states

**6.2.1.1.1 state F1 (Inactive)**: In this inactive (powered-off) state, the TE is not transmitting and cannot detect the presence of any input signals. In the case of locally powered TEs which cannot detect the appearance/disappearance of power source 1 or 2, this state is entered when local power is not present. For TEs that can detect power source 1 or power source 2, this state is entered whenever loss of power (required to support all TEI functions) is detected, or when the absence of power from power source 1 or 2, whichever power source is used for determining the connection status, is detected.

**6.2.1.1.2 state F2 (Sensing)**: This state is entered after the TE has been powered on but has not determined the type of signal (if any) that the TE is receiving. When in this state, a TE may go to a low-power consumption mode as specified in 5.1.8.

**6.2.1.1.3 state F3 (Deactivated)**: This is the deactivated state of the physical protocol. Neither the NT nor the TE is transmitting. When in this state, a TE may go to a low-power consumption mode as specified in 5.1.8.

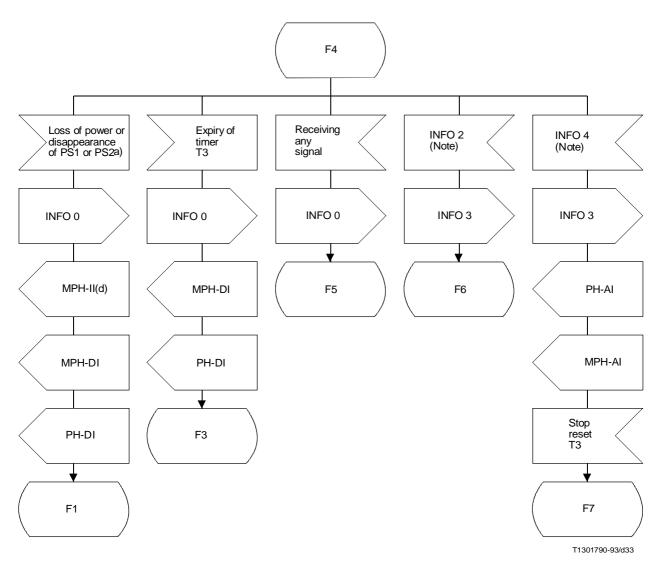

**6.2.1.1.4 state F4 (Awaiting signal)**: When the TE is requested to initiate activation by means of a PH-ACTIVATE request primitive, it transmits a signal (INFO 1) and waits for a response from the NT.

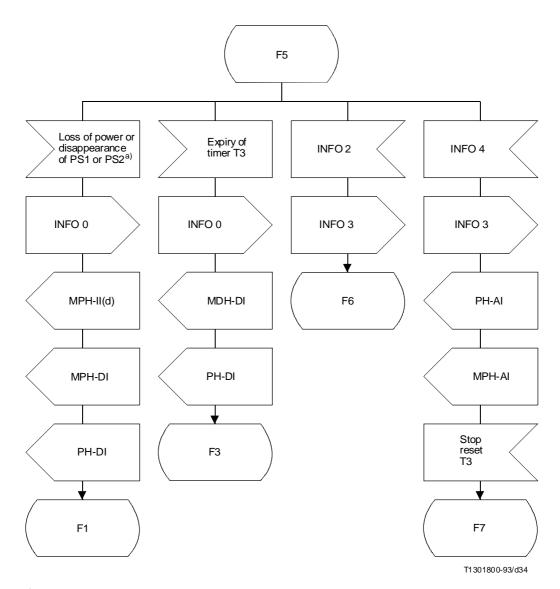

**6.2.1.1.5 state F5 (Identifying input)**: At the first receipt of any signal from the NT, the TE ceases to transmit INFO 1 and awaits identification of signal INFO 2 or INFO 4.

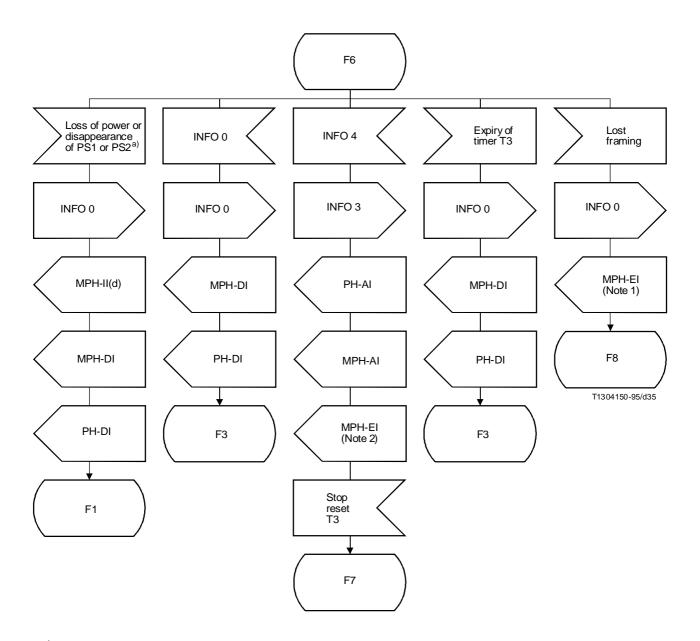

**6.2.1.1.6 state F6 (Synchronized)**: When the TE receives an activation signal (INFO 2) from the NT, it responds with a signal (INFO 3) and waits for normal frames (INFO 4) from the NT.

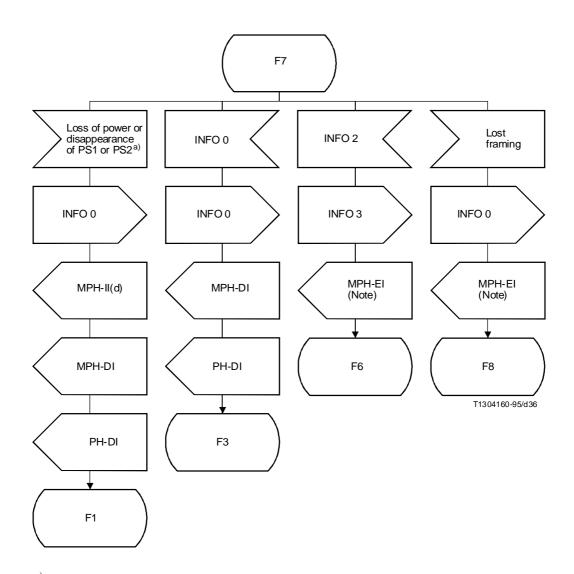

**6.2.1.1.7 state F7** (**Activated**): This is the normal active state with the protocol activated in both directions. Both the NT and TE are transmitting normal frames. State F7 is the only state where B- and D-channel contain operational data.

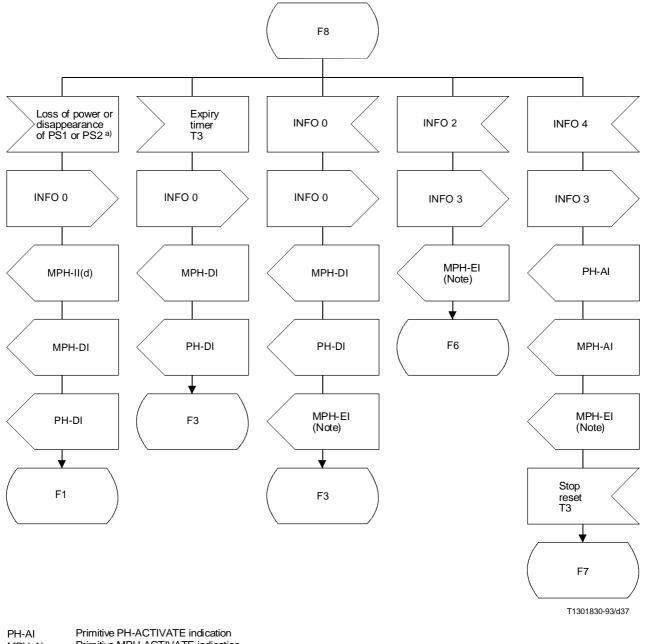

**6.2.1.1.8 state F8 (Lost framing)**: This is the condition when the TE has lost frame synchronization and is awaiting re-synchronization by receipt of INFO 2 or INFO 4 or deactivation by receipt of INFO 0.

## 6.2.1.2 NT states

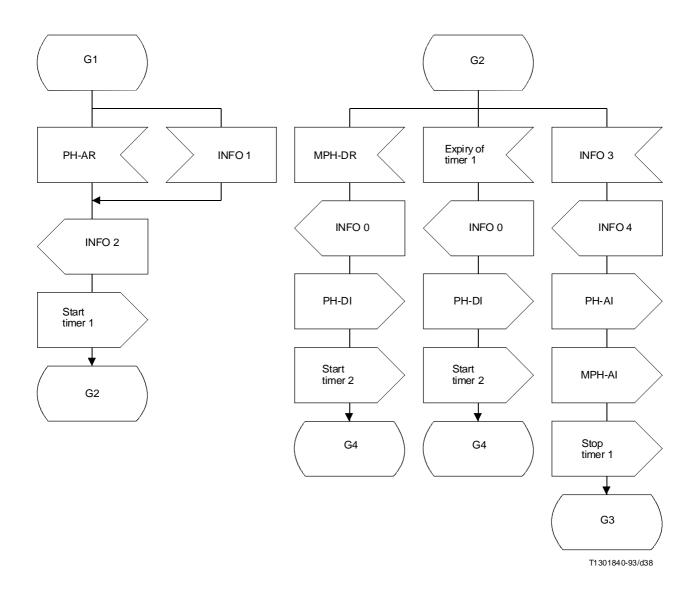

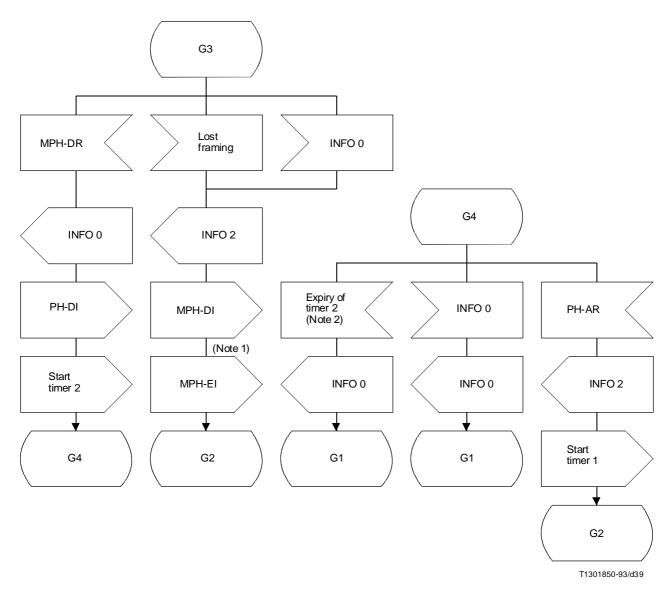

**6.2.1.2.1 state G1 (Deactivated)**: In this deactivated state, the NT is not transmitting. When in this state, an NT may go to a low-power consumption mode as specified in 5.1.8.

#### 10 **Recommendation I.430** (11/95)

**6.2.1.2.2 state G2 (Pending activation**): In this partially active state, the NT sends INFO 2 while waiting for INFO 3. This state will be entered on request by higher layers, by means of a PH-ACTIVATE request primitive, or on the receipt of INFO 0 or lost framing while in the active state (G3). The choice to eventually deactivate is up to higher layers within the NT.

**6.2.1.2.3 state G3 (Activated)**: This is the normal active state where the NT and TE are active with INFO 4 and INFO 3, respectively. A deactivation may be initiated by the NT system management, by means of an MPH-DEACTIVATE request primitive, or the NT may be in the active state all the time, under non-fault conditions.

**6.2.1.2.4 state G4 (Pending deactivation)**: When the NT wishes to deactivate, it may wait for a timer to expire before returning to the deactivated state.

## 6.2.1.3 Activate primitives

The following primitives should be used between layers 1 and 2 and between layer 1 and the management entity in the activation procedures. For use in state diagrams, etc., abbreviations of the primitive names are also given.

- PH-ACTIVATE request (PH-AR);

- PH-ACTIVATE indication (PH-AI);

- MPH-ACTIVATE indication (MPH-AI).

## 6.2.1.4 Deactivate primitives

The following primitives should be used between layers 1 and 2 and between layer 1 and the management entity in the deactivation procedures. For use in state diagrams, etc., abbreviations of the primitive names are also given.

- PH-DEACTIVATE indication (PH-DI);

- MPH-DEACTIVATE request (MPH-DR);

- MPH-DEACTIVATE indication (MPH-DI).

## 6.2.1.5 Management primitives

The following primitives should be used between layer 1 and the management entity. For use in state diagrams, etc., abbreviations of the primitive names are also given.

• MPH-ERROR indication (MPH-EI):

Message unit contains type of error or recovery from a previously reported error.

• MPH-INFORMATION indication (MPH-II):

Message unit contains information regarding the physical layer conditions. Two parameters are provisionally defined: connected and disconnected.

NOTE – Implementation of primitives in NTs and TEs is not for recommendation.

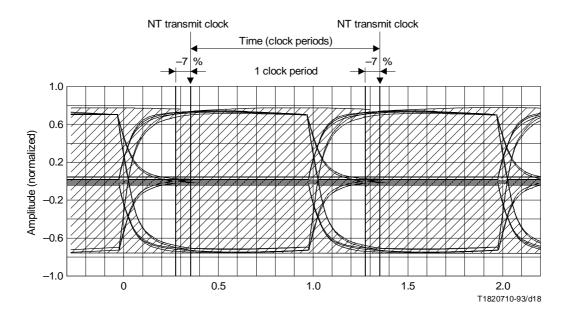

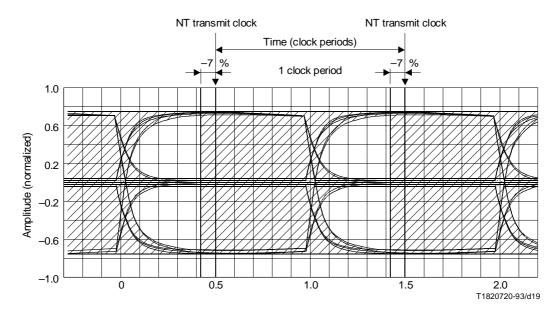

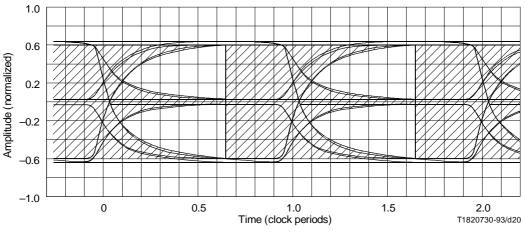

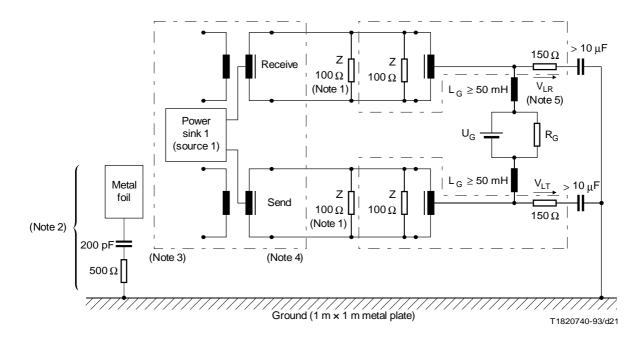

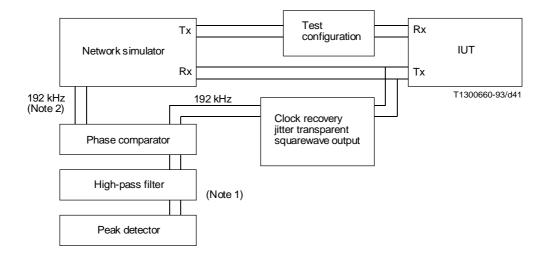

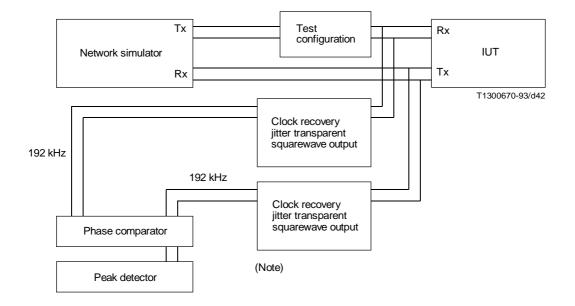

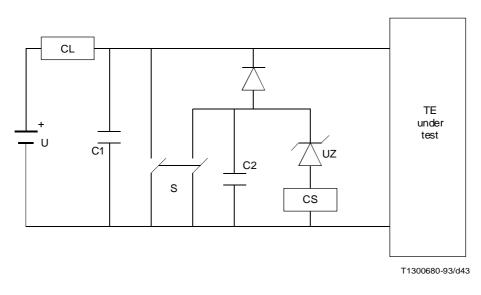

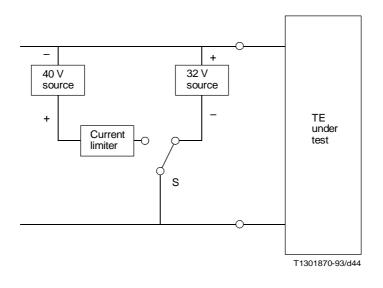

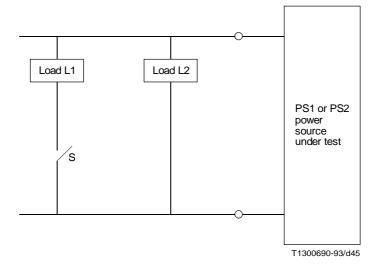

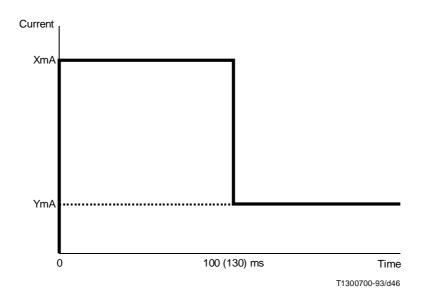

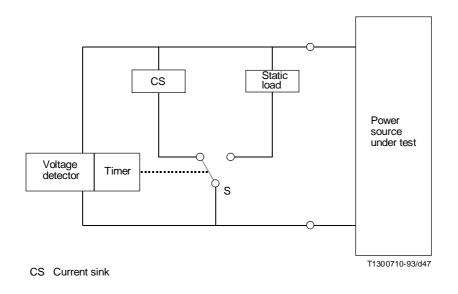

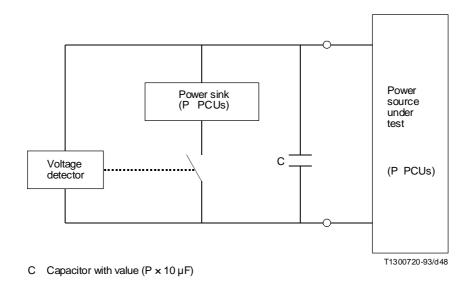

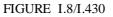

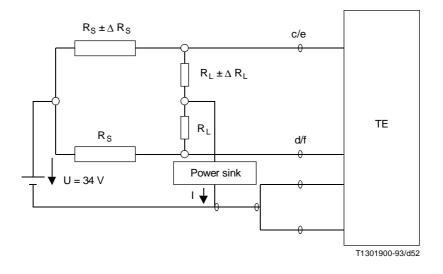

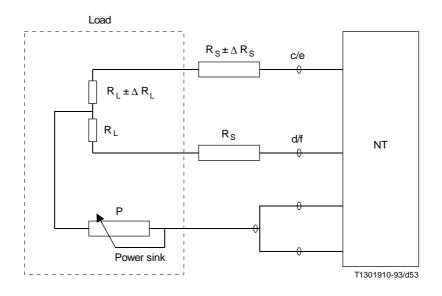

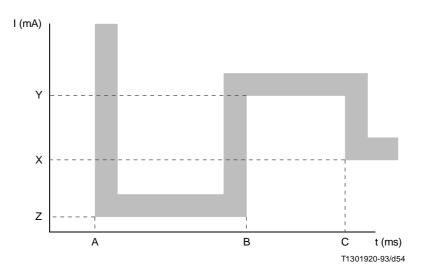

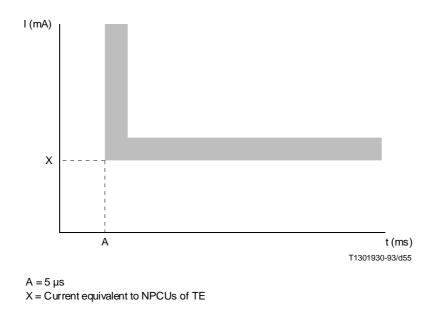

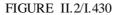

#### 6.2.1.6 Valid primitive sequences